# I/O Pin Characteristics - Absolute Maximums

- Don't operate near the absolute maximums.

- Beyond these points, damage is likely to occur.

#### 37.1.1 Absolute Maximum Ratings

Stresses beyond those listed in Table 37-1 on page 74 under may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 37-1. Absolute maximum ratings.

| Symbol           | Parameter                                                      | Condition | Min. | Тур. | Max.                 | Units |  |

|------------------|----------------------------------------------------------------|-----------|------|------|----------------------|-------|--|

| V <sub>cc</sub>  | Power supply voltage                                           |           | -0.3 |      | 4                    | V     |  |

| Ivcc             | Current into a V <sub>CC</sub> pin 20                          |           | 200  | mA   |                      |       |  |

| I <sub>GND</sub> | Current out of a Gnd pin                                       |           |      |      | 200                  | mA    |  |

| V <sub>PIN</sub> | Pin voltage with respect to Gnd and $\mathrm{V}_{\mathrm{CC}}$ |           | -0.5 |      | V <sub>CC</sub> +0.5 | V     |  |

| I <sub>PIN</sub> | I/O pin sink/source current                                    |           | -25  |      | 25                   | mA    |  |

| T <sub>A</sub>   | Storage temperature                                            |           | -65  |      | 150                  | °C    |  |

| Tj               | Junction temperature                                           |           |      |      | 150                  | C     |  |

#### Figure 1: Absolute Ratings

# $\rm I/O$ Pin Characteristics - General Operating Specifications

## For specifications be met (electrical and timing), these must be obeyed.

#### 37.1.2 General Operating Ratings

The device must operate within the ratings listed in Table 37-2 in order for all other electrical characteristics and typical characteristics of the device to be valid.

#### Table 37-2. General operating conditions.

| Symbol           | Parameter             | Condition | Min. | Тур. | Max. | Units |  |

|------------------|-----------------------|-----------|------|------|------|-------|--|

| V <sub>cc</sub>  | Power supply voltage  |           | 1.60 |      | 3.6  | V     |  |

| AV <sub>CC</sub> | Analog supply voltage |           | 1.60 |      | 3.6  |       |  |

| T <sub>A</sub>   | Temperature range     |           | -40  |      | 85   | °C    |  |

| Tj               | Junction temperature  |           | -40  |      | 105  | C     |  |

### Figure 2: General Operating Conditions

# I/O Pin Characteristics - Pin Specifications

Table 37-7. I/O pin characteristics.

| Symbol                                                             | Parameter                         | Condition                    |                              | Min.                  | Тур.                 | Max.                 | Units |

|--------------------------------------------------------------------|-----------------------------------|------------------------------|------------------------------|-----------------------|----------------------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current       |                              |                              | -20                   |                      | 20                   | mA    |

|                                                                    | High level input voltage          | V <sub>CC</sub> = 2.7 - 3.6V |                              | 2                     |                      | V <sub>CC</sub> +0.3 |       |

| $V_{\rm IH}$                                                       |                                   | V <sub>CC</sub> = 2.0 - 2.7V |                              | 0.7*V <sub>CC</sub>   |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    |                                   | V <sub>CC</sub> = 1.6 - 2.0V |                              | 0.7*V <sub>CC</sub>   |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    | Low level input voltage           | V <sub>CC</sub> = 2.7- 3.6V  |                              | -0.3                  |                      | 0.3*V <sub>CC</sub>  |       |

| VIL                                                                |                                   | V <sub>CC</sub> = 2.0 - 2.7V |                              | -0.3                  |                      | 0.3*V <sub>CC</sub>  |       |

|                                                                    |                                   | V <sub>CC</sub> = 1.6 - 2.0V |                              | -0.3                  |                      | 0.3*V <sub>CC</sub>  | v     |

|                                                                    | High level output voltage         | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OH</sub> = -2mA       | 2.4                   | 0.94*V <sub>CC</sub> |                      |       |

|                                                                    |                                   | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OH</sub> = -1mA       | 2.0                   | 0.96*V <sub>CC</sub> |                      |       |

| V                                                                  |                                   |                              | I <sub>OH</sub> = -2mA       | 1.7                   | 0.92*V <sub>CC</sub> |                      |       |

| V <sub>OH</sub>                                                    |                                   | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -8mA       | 2.6                   | 2.9                  |                      |       |

|                                                                    |                                   | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -6mA       | 2.1                   | 2.6                  |                      |       |

|                                                                    |                                   | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -2mA       | 1.4                   | 1.6                  |                      |       |

|                                                                    | Low level output voltage          | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OL</sub> = 2mA        |                       | 0.05*V <sub>CC</sub> | 0.4                  |       |

|                                                                    |                                   | V <sub>cc</sub> = 2.3 - 2.7V | I <sub>OL</sub> = 1mA        |                       | 0.03*V <sub>CC</sub> | 0.4                  |       |

|                                                                    |                                   | Low level output voltage     | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OL</sub> = 2mA |                      | 0.06*V <sub>CC</sub> | 0.7   |

| V <sub>OL</sub>                                                    |                                   | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 15mA       |                       | 0.4                  | 0.76                 |       |

|                                                                    |                                   | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 10mA       |                       | 0.3                  | 0.64                 |       |

|                                                                    |                                   | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 5mA        |                       | 0.3                  | 0.46                 |       |

| I <sub>IN</sub>                                                    | Input leakage current             |                              |                              |                       | < 0.001              | 0.1                  | μA    |

| Rp                                                                 | I/O pin Pull/Buss keeper resistor |                              |                              |                       | 25                   |                      | kΩ    |

| R <sub>RST</sub>                                                   | Reset pin pull-up resistor        |                              |                              |                       | 25                   |                      | N12   |

| t,                                                                 | Pad rise time                     | No load                      |                              |                       | 4.0                  |                      | ns    |

| L <sub>r</sub>                                                     |                                   | No load                      | slew rate limitation         |                       | 7.0                  |                      | iis   |

Figure 3: I/O Pin Specifications, Contractions - Contractions

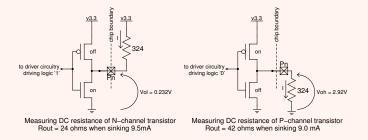

# I/O Pin Characteristics - RDSout

- The lol and loh specifications beg the question of actual DC output resistance.

- These values are easily found with a simple setup.

- The lower resistance of the N-channel transistor becomes evident when testing the I/O pin with a 50 ohm transmission. (later)

Figure 4: I/O Pin DC Equivalent Output Resistance

▲□▶ ▲圖▶ ▲国▶ ▲国▶ 三国 - 釣A@

# I/O Pin Characteristics - PINnCTRL

- Each I/O pin has its own PINnCTRL register.

- PINnCTRL controls:

- Output and Pull Configuration 8 choices

- Slew Rate Limit fast or slow edges

- Inverted I/O inverted I/O or not

- Input and Sense Configuration mostly for interrupts

- The following schematics are not the actual circuitry of the xmega chip, but they are logically and electrically correct conceptual drawings of how each I/O configuration operates.

- In particular, a 24K resistor would be too costly from a area standpoint on silicon. The pullup and pulldown resistances are most likely implemented with weak (big L, small W) transistors.

- Each I/O configuration was lab tested for their electrical and logical functionality. The assumption is that nothing is connected to Pn. Electrical characteristics for each configuration were tested as follows:

- Test for each Pn=Z case:

- Connect 24K resistor from Pn to Vdd. Pn should be at Vdd.

- Connect 24K resistor from Pn to Vss. Pn should be at Vss.

- Test for each Pn=0R case (logic '0' resistive):

- Connect 24K resistor from Pn to Vdd. Pn should be at Vdd/2.

- Test for each Pn=1R case: (logic '1' resistive)

- Connect 24K resistor from Pn to Vss. Pn should be at Vdd/2.

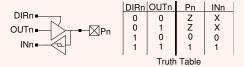

▶ Totem pole configuration able to source and sink current from Pn.

Bi-directional, depending on the setting of the DIRn bit

\\set port B bit zero to totem pole

PORTB.PINOCTRL = PORT\_OPC\_TOTEM\_gc;

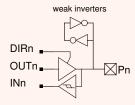

Figure 5: Totem Pole I/O

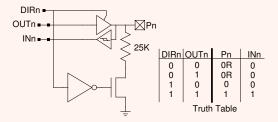

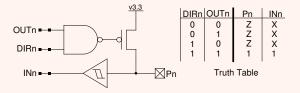

- Totem pole with pulldown is a totem pole configuration that depending on the DIRn bit, the input may be pulled down with a 25K resistance.

- Bi-directional, can sink or source current

\\set port B bit zero to totem pole with pulldown

PORTB.PINOCTRL = PORT\_OPC\_PULLDOWN\_gc;

Figure 6: Totem Pole with Pulldown

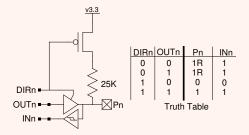

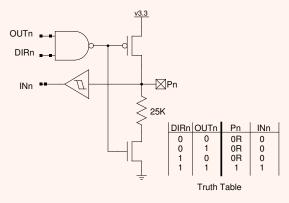

- Totem pole with pullup is like the totem pole configuration but depending upon the DIRn bit, the input may be pulled up with a 25K resistance.

- Bi-directional, can sink or source current.

\\set port B bit zero to totem pole with pullup

PORTB.PINOCTRL = PORT\_OPC\_PULLUP\_gc;

Figure 7: Totem Pole with Pullup

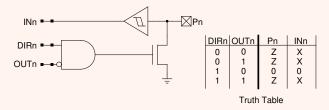

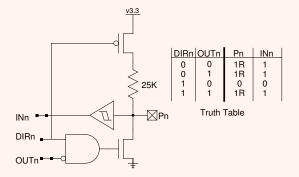

- Totem pole with bus keeper keeps the last value seen on PINn if driven from the output driver or external circuitry.

- ▶ The input will be pulled up or down with a 25K resistance

- Bi-directional, can sink or source current

- When selected, the bus keeper is active, regardless of the value of the DIRn bit

```

\\set port B bit zero to totem pole with bus keeper

PORTB.PINOCTRL = PORT_OPC_BUSKEEPER_gc;

```

| DIRn                   | OUTn | Pn  | INn |  |  |  |

|------------------------|------|-----|-----|--|--|--|

| 0                      | 0 0  |     | Pn⁻ |  |  |  |

| 0 1                    |      | Pn⁻ | Pn⁻ |  |  |  |

| 1                      | 0    | 0   | 0   |  |  |  |

| 1                      | 1    | 1   | 1   |  |  |  |

| Bug Koopor Truth Table |      |     |     |  |  |  |

Bus Keeper Truth Table

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ のへで

\*Pn : last value impressed on Pn

Figure 8: Bus Keeper

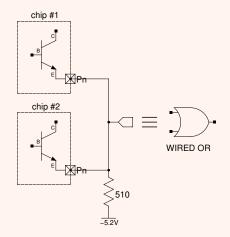

- Wired OR configuration is only able to source current

- When the DIRn bit is logic zero, the input buffer is floating.

- The wired OR is technically bi-directional, but can only source current.

\\set port B bit zero to wired OR

PORTB.PINOCTRL = PORT\_OPC\_WIREDOR\_gc;

Figure 9: Wired OR

Wired OR with Pulldown differs from Wired OR in that when the DIRn bit is logic zero, the input buffer is pulled down by a nominal 25K resistance

\\set port B bit zero to wired OR with a pulldown resistance

PORTB.PINOCTRL = PORT\_OPC\_WIREDORPULL\_gc;

Figure 10: Wired OR with Pulldown

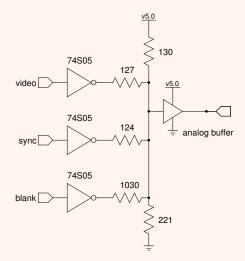

Wired AND configuration is bi-directional and only able to sink current

Figure 11: Wired AND

Wired AND configuration is bi-directional and only able to sink current

Figure 12: Wired And with Pullup

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

Figure 13: Wired OR as used in Emitter Coupled Logic

▲□▶ ▲圖▶ ▲≣▶ ▲≣▶ = 差 - 釣��

Figure 14: Wired AND VGA Level Generator in STTL Logic

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三三 のへで

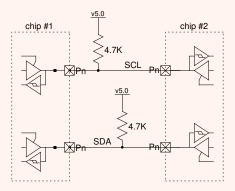

- I2C interface uses wired AND configuration

- Any I/O can pull the SCL or DAT line down without conflict.

- Any I/O can be a driver or receiver

- External pullups must be used for pull the lines up.

- Pullups must be sized to pull up capacitance on the signaling lines

Figure 15: I2C Interface using Wired AND Configuration

- Each I/O pin has a SRLEN bit within its PINnCTRL.

- SRLEN controls how much current the pin can supply on an edge.

- It does not effect the DC current capability of the pin.

- When set, the pin is limited to a 7ns rise and fall time.

- When clear, the pin operates with a 4ns rise and fall time.

- Spec is written for no load.

|    | Pad rise time | No load |                      | 4.0 | -  |  |

|----|---------------|---------|----------------------|-----|----|--|

| 4r |               |         | slew rate limitation | 7.0 | ns |  |

Figure 16: Slew Rate Control Specification

▲□▶ ▲□▶ ▲三▶ ▲三▶ 三 シの()

### Lab measurements

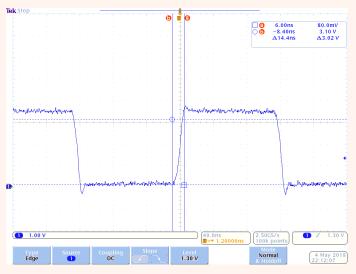

### Figure 17: Slew Rate Control On

### Lab measurements

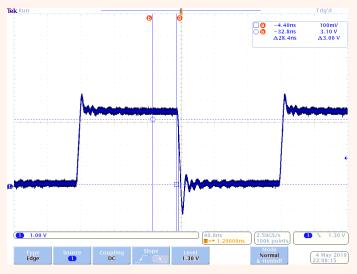

#### Figure 18: Slew Rate Control Off

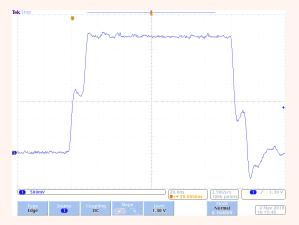

- Lab measurements clearly indicate that the I/O pins are incapable of incident-wave switching

- A point-to-point connection on a 50 ohm line is however possible.

- Scope probe is at the I/O pin

Figure 19: I/O pin driving 50 ohm transmission line

-

# I/O Pin Characteristics - Output impedance

Lab measurements would indicate the dynamic output resistance is approximately 50 ohms

◆□▶ ◆□▶ ◆三▶ ◆三▶ 三三 のへで